# **VMware, Inc.** 3401 Hillview Ave, Palo Alto, CA 94304, USA, www.vmware.com

# TOE Design (ADV\_TDS.3): VMM Subsystem VMware ESXi 8.0

| Author:  | VMware     |

|----------|------------|

| Version: | 1.0        |

| Date:    | 2022-08-10 |

| Cert-ID: |            |

|          |            |

Company: VMware, Inc.

Version 1.0

# **M**Ware<sup>®</sup>

VMware, Inc. 3401 Hillview Ave Palo Alto, CA 94304 United States of America

http://www.vmware.com

Copyright © 1998 - 2022 VMware, Inc. All rights reserved. This product is protected by copyright and intellectual property laws in the United States and other countries as well as by international treaties. VMware products are covered by one or more patents listed at <a href="http://www.vmware.com/go/patents">http://www.vmware.com/go/patents</a>.

VMware is a registered trademark or trademark of VMware, Inc. in the United States and other jurisdictions. All other marks and names mentioned herein may be trademarks of their respective companies.

# **Revision History**

| Version | Description of changes | Modified by    | Date       |

|---------|------------------------|----------------|------------|

| 1.0     | Initial Draft Version  | Nicholas Leuci | 2022-08-10 |

|         |                        |                |            |

|         |                        |                |            |

|         |                        |                |            |

#### **Table of Contents**

#### Contents

| R | evisio                                                                                                                              | on History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 3                                                                                                                                          |

|---|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Intr                                                                                                                                | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 6                                                                                                                                          |

| 2 | Sul                                                                                                                                 | bsystems of the TOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 7                                                                                                                                          |

|   | 2.1                                                                                                                                 | Interaction between sub-systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                              |

|   | 2.2                                                                                                                                 | Subsystem AAA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

|   | 2.3                                                                                                                                 | Subsystem BBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

|   | 2.4                                                                                                                                 | Subsystem CCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

|   |                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                              |

| 4 |                                                                                                                                     | ual Machine Monitor (VMM) Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                              |

|   | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.4<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.2.7<br>4.2.2<br>4.2.4<br>4.2.8<br>4.2.6<br>4.2.7 | VMM Hardware Virtualization (SFR-ENFORCING)         1 Security Functionality (SF)         2 Security Functional Requirement (SFR)         3. Provided TSFI         1.4.1 Internal Interfaces (Context-switching between VMM and VM)         1.4.2 Internal Interfaces (Sensitive host fields for context-switch)         1.4.3 Internal Interfaces (Sensitive host field for posted interrupts)         1.4.4 Internal Interfaces (Controls determining circumstances causing HV exits)         5 Used interfaces of other modules.         6 Mapping to the Source Code         7 Appendix A: Bibliography for the Intel VT References.         8 Appendix B: Navigating HV module code         VMM HV Memory Management (SFR-ENFORCING)         1 Security Functionality (SF)         2 Security Functional Requirement (SFR)         2.3 Provided TSFI         2.4.1 Internal Interfaces of the Module (General execution)         2.4.2 Internal Interfaces of the Module (VNPT, for nested guest memory virtualization)         5 Used interfaces of other modules.         6 Mapping to the Source Code | 13<br>13<br>14<br>16<br>17<br>18<br>20<br>21<br>22<br>23<br>23<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26 |

|   | 4.3.2<br>4.3.2<br>4.3.4<br>4.3.4<br>4.3.5<br>4.3.6<br><b>4.4</b>                                                                    | VMM Host Interrupts IDT, APIC, MAP (SFR-ENFORCING)         1 Security Functionality (SF)         2 Security Functional Requirement (SFR)         3 Provided TSFI         3.4.1 Internal Interfaces of the Module         4 Used interfaces of other modules         5 Mapping to the Source Code         6 Appendix A: Navigating Interrupt Optimization Module Code         VMM Hot Path (SFR-NON-INTERFERING)         1 Mapping to the Source Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37<br>37<br>37<br>37<br>38<br>38<br>38<br>39<br><b>40</b>                                                                                    |

|   | 4.5                                                                                                                                 | VMM Instruction Emulation (SFR-NON-INTERFERING)<br>1 Mapping to the Source Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41                                                                                                                                           |

| 4.5.2 Appendix A: Published Technical Research Bibliography                                                                                              | 42       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.6 VMM Guest Interrupts (SFR-NON-INTERFERING)                                                                                                           |          |

| <ul> <li>4.7 VMM Timekeeping (SFR-NON-INTERFERING)</li></ul>                                                                                             |          |

| 4.8 [vmKernel] VMM-VMK (SFR- ENFORCING)                                                                                                                  |          |

| <ul> <li>4.8.1 Security Functionality (SF)</li> <li>4.8.2 Security Functional Requirement (SFR)</li> <li>4.8.3 Provided TSFI</li> </ul>                  | 46       |

| 4.8.4.1 Internal Interfaces of the Module (World-Switch: Model-Specific Registers)<br>4.8.4.2 Internal Interfaces of the Module (World-Switch: VT State) | 47       |

| 4.8.4.3 Internal Interfaces of the Module (VMKCall: State Flushing)<br>4.8.5 Used interfaces of other modules                                            | 50<br>51 |

| 4.8.6 Mapping to the Source Code<br>4.8.7 Appendix A: Navigating VMM-VMK Entry Module Code                                                               |          |

| 4.9 VMM SGX (SFR-NON-INTERFERING)                                                                                                                        | 55       |

| <ul><li>4.9.1 Mapping to the Source Code (Interpreter support)</li><li>4.9.2 Appendix A: Bibliography for the Intel SGX References</li></ul>             | 56       |

# 1 Introduction

This document contains a description of the TOE Design, which is required by ADV\_TDS.3. Thereby the TOE is subdivided in terms of subsystems and modules,

# 2 Subsystems of the TOE

Subsystem: High-Level Description of the different parts oft he TOE. It needs to be described what the main purpose of the subsystem and how.

Module: Additional subdivision of the subsystems and a More detailed description about their Implementation (e.g., based on libraries)

For each sub system (all are at high level):

- High level Subsystem description

- Near source code level description

- Need to write SFRs security enforcing, supporting and non-interfering

- Not in near source code level detail for parts of subsystem that are related to non-interfering SFRs

- Modules that are non-interfering, don't need to be described in near-source code level detail.

The TOE can be subdivided into the following subsystems:

- Subsystem AAA Here a short description about the purpose of the subsystem should be entered.

- Subsystem BBB Here a short description about the purpose of the subsystem should be entered.

- Subsystem CCC Here a short description about the purpose of the subsystem should be entered.

- ...

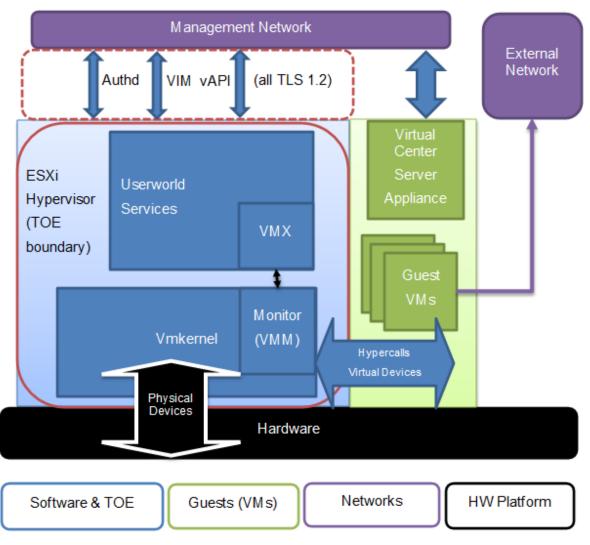

The figure below gives an overview about the architecture of the TOE and how the TOE can be subdivided into Subsystems and modules

Put the detailed figures of the overall TOE. Put the low-level-ESXI architecture document. How we draw the boundaries of modules in the sub-system is up to us. Multiple images will be supplied.

#### 2.1 Interaction between sub-systems

Figure 1: TOE Subsystems and Modules

Please give a short explanation of Figure 1. Thereby especially the purpose and the interactions between the subsystems should be explained.

#### 2.2 Subsystem AAA

Detailed Description of the purpose and content of subsystem AAA. Each group adds their own subsystem section.

Still high-level description – half a page to one-to-two page level. Overview of which modules are in the subsystem; how the modules relate to each other. Overview of APIs of modules, i.e., communication between VMkernel and Monitor.

#### 2.3 Subsystem BBB.

Detailed Description of the purpose and content of subsystem BBB. Each group adds their own subsystem section.

### 2.4 Subsystem CCC

Detailed Description of the purpose and content of subsystem CCC. Each group adds their own subsystem section.

# 4 Virtual Machine Monitor (VMM) Subsystem

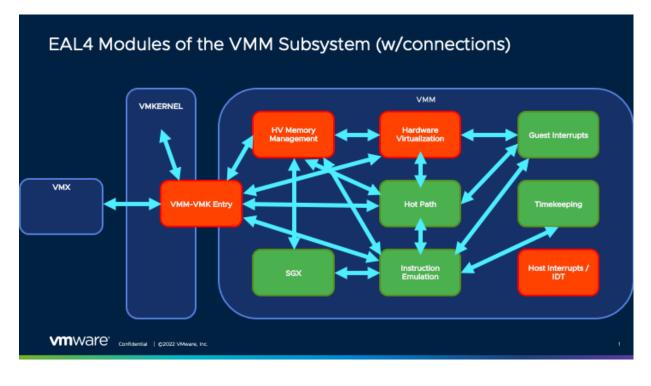

#### A. Subsystem Diagram

| SFR Color | Red –    | Enforcing modules       |

|-----------|----------|-------------------------|

| Encoding  | Yellow - | Supporting modules      |

| Legend:   | Green –  | Non-Interfering modules |

#### B. High Level Summary

The Virtual Machine Monitor (hereafter "VMM") is a kernel-mode program responsible for execution of virtual CPUs. One VMM program instance exists per VM. One VMM world (thread) exists for each virtual CPU in a VM.

VMM presents virtual hardware to the virtual machine and causes its virtual CPUs to make progress in execution, in a high-performance manner, with proper isolation and security. VMM relies on hardware virtualization (via Intel's VT) and, to a lesser extent, instruction emulation for this purpose.

VMM exposes virtual hardware to VM software and handles the edges of this interaction, including virtual interrupts and virtualized device access. VMM exposes memory to a VM as well. As such, VMM is responsible for managing views of memory.

VMM also implements and supports various virtualization features. Some features include nested virtualization (such that a VM can, internally, run a nested VM) and virtualization of CPU features such as secure enclave execution via Intel's SGX.

VMM interacts with other software in the TOE by switching to the vmKernel when required. VMM cooperates with the vmKernel (vmKernel RM CPU Subsystem) to share the host CPU Version 1.0 10 (as both pieces of software are kernel-mode, privileged software). VMM is largely subordinate to the vmKernel, as the vmKernel RM CPU Subsystem decides scheduling of host worlds such as those worlds running VMM.

#### C. List of Modules

| Module Name                | Brief Description                                                                                                                                                                                                    | Security Type       |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Hardware<br>Virtualization | Support for Intel's VT CPU virtualization support, both for regular VMs and those containing nested VMs. Manages and executes context-switching between VMM software in the TOE and the Virtual Machine domain (VM). | SFR-ENFORCING       |

| HV Memory<br>Management    | Virtualization of guest memory including presentation of vmKernel-provided memory to the VM and any nested VMs run inside.                                                                                           | SFR-ENFORCING       |

| VMM/VMK<br>Entry           | Context-switching between VMM and the vmKernel and associated optimizations.                                                                                                                                         | SFR-ENFORCING       |

| Host<br>Interrupt/IDT      | Optimized Inter-Processor Interrupt support for fast synchronous signaling between VCPUs of a single VM.                                                                                                             | SFR-ENFORCING       |

| SGX                        | Virtualization of Intel Software Guard Extensions support for secure enclaves.                                                                                                                                       | SFR-NON-INTERFERING |

| Guest Interrupts           | VM-internal virtual interrupt support, including delivery of virtual interrupts to virtual VCPUs for consumption in the VM.                                                                                          | SFR-NON-INTERFERING |

| Instruction<br>Emulation   | Correct emulation of instructions, as a fallback when fast<br>handling of a VT exit is impossible, or emulation is<br>otherwise required.                                                                            | SFR-NON-INTERFERING |

| Hot Path                   | Fast handling of VT exits from the Hardware Virtualization module.                                                                                                                                                   | SFR-NON-INTERFERING |

| Timekeeping                | Management of VM-perceived time.                                                                                                                                                                                     | SFR-NON-INTERFERING |

#### 4.1 VMM Hardware Virtualization (SFR-ENFORCING)

The VMM Hardware Virtualization (hereafter "HV") module runs as part of the Virtual Machine Monitor (part of the TOE, a kernel-mode program with one instance per VM, hereafter "VMM"). The HV module implements execution of the virtual machine domain (guest OS, hereafter "VM" or "guest") by use of Hardware Virtualization ("HV") provided by the Intel CPU Virtualization Technology (known by Intel as "VMX" but hereafter referred to by the VMware term, "VT"). The HV module manages CPU and VT state, and handles switches to and from VM execution, for various reasons.

Once initialized, the HV module runs in a loop:

1. enter VM execution (hereafter known as an "HV resume"),

- 2. wait for the CPU to exit VM execution and return to VMM (hereafter known as an "HV exit"),

- 3. determine from exit description what handler to run,

- 4. call that handler,

- 5. and likely return to the first step: HV resume.

The HV module is responsible for isolating the VM from the VMM (and other host software). This isolation is implemented two ways: (1) by careful constraint of and description of VM execution using VT state and (2) by careful context-switching of CPU state, avoiding undesirable effects upon VMM (and other host software).

VT contains a Virtual Machine Control Structure (hereafter "VMCS") which defines state for the CPU to load upon HV resume and HV exit, as well as controls constraining VM execution and under what conditions HV exits shall occur. The HV module programs the VMCS accordingly. Intel describes the VMCS, VT and related information in Intel Software Developers Manual, Volume 3C: System Programming Guide, Part 3, Chapters 23-27 and 30 (See 4.1,7 Appendix A below).

The HV module is responsible for context-switching of VM state. This context-switching occurs in different ways, at different points in code: at HV resume and HV exit (automatically via VT), in code paths immediately before HV resume and after HV exit (in software, via the HV module), and in deferred code paths transitioning between pieces of software in the TOE (in the VMM/VMK Entry Module, 4.8).

Because the VMCS defines when the VM may cause HV exits, and because the HV module must context-switch VM CPU state (which could, unswitched, affect other software in the TOE), the HV module is SFR-enforcing for FPT\_VIV\_EXT.1.1. Because the handling of HV exits (which could, handled incorrectly, affect other software in the TOE) is implemented in the HV module, it is SFR-enforcing for FPT\_VIV\_EXT.1.2.

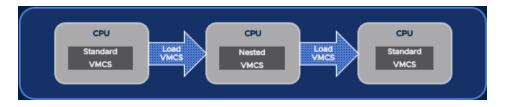

The HV module implements nested virtualization support, allowing a VM run encapsulated VMs of its own. The module implements Virtualized Hardware Virtualization (hereafter "VHV") and specifically for Intel, it implements Virtual VT (hereafter "VVT"). VHV is supported for Microsoft Windows guests using Hyper-V, which rely upon an implementation of VT (here, our VVT) for the Microsoft implementation of Virtualization-Based Security.

When VVT is in use, the guest software is split conceptually into two parts: the inner hypervisor (which programs and uses VVT via VT semantics) and the inner guest (which runs under control of the HV module, with additional description and constraints added by the inner hypervisor). For performance, the HV module uses two VMCS structures when running with VVT: a standard VMCS and a nested VMCS. The standard VMCS describes and constrains the inner hypervisor, while the nested VMCS describes and constrains the inner guest. Only one VMCS is active at a given time, with transitions and management of VMCS state optimized carefully.

When a VMCS is not in active use, its values may be modified by live execution (e.g. the inner hypervisor writing new configuration to the nested VMCS to constrain the inner guest).

The HV module maintains an in-memory cache of nested VMCS state and tracks dirty subportions of this cache, deferring recomposition of the nested VMCS until just before its live use.

When switching between executing the inner hypervisor and the inner guest, HV controls must be updated in the VMCS that is about to become active. This update carefully composes as safe VMCS. When transitioning to executing the inner guest, the VMCS combines the wishes of the inner hypervisor (as described in the nested VMCS) and the requirements of the HV module (as described in the standard VMCS).

For performance reasons, some VMCS fields allow the guest (be it the inner hypervisor or the inner guest) to access certain CPU resources directly, without exiting to the HV module. Such resources are those which are either inherently harmless to the TOE (e.g. guest general-purpose registers) or those which are context-switched carefully shortly after HV exit (e.g. side-channel mitigation model-specific registers which do no harm to execution of the TOE during the brief moment between HV exit and context-switching).

VT's VMCS contains controls and structures related to guest-visible memory. That state and its management is handled by The VMM HV Memory Module (4.2).

HV exit handling in the HV module will call into other modules, depending upon the exit condition.

The HV module cannot be disabled and is always used in the running of VMs.

#### 4.1.1 Security Functionality (SF)

See the table in Section 4.1.2.

#### 4.1.2 Security Functional Requirement (SFR)

| Security Function (SF)         Security Function<br>Requirement (SFR)           SF6.Protection of the TSF<br>(FPT)         FPT_VIV_EXT.1.1 |                 | Rationale                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                            |                 | The TSF shall maintain a security domain for the execution of each virtual machine that protects the virtual machine from interference and tampering by untrusted subjects or subjects from outside the scope of the VM. |

| SF6.Protection of the TSF (FPT)                                                                                                            | FPT_VIV_EXT.1.2 | The TSF shall enforce separation between the security domains of VMs in the TSC.                                                                                                                                         |

#### 4.1.3. Provided TSFI

This module has no TSFI as it is an internal module and has no exposure to outside the TOE.

### 4.1.4.1 Internal Interfaces (Context-switching between VMM and VM).

| Module Function                 | Security<br>Function(s)               | SFR(s)          | Parameters | Return Value                                                                      | Rationale                                                                                                                                                      |

|---------------------------------|---------------------------------------|-----------------|------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HVResume                        | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.1.1 | None       | None. Does not<br>return to caller.<br>Exits at VMCS<br>HOST_RIP.                 | Main entry<br>point to HV<br>resume<br>functionality<br>in VMM.                                                                                                |

| HV_StepToSafePointAndRes<br>ume | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.1.1 | None       | <b>None</b> . Does not<br>return to caller.<br>Exits at VMCS<br>HOST_RIP.         | Alternate<br>path to call<br>VMM<br>Instruction<br>Emulation<br>Module (see<br>4.5), then<br>program<br>VMCS with<br>VMM state<br>and<br>proceed to<br>resume. |

| HVVendorSpecificResume          | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.1.1 | None       | <b>None</b> . Does not<br>return to caller.<br>Exits at VMCS<br>HOST_RIP.         | Program<br>VMCS with<br>VM state<br>(program<br>counter,<br>stack<br>pointer,<br>CPU flags,<br>pending<br>interrupt<br>information<br>if any)                  |

| HVMSR_VMEnter                   | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.1.1 | None       | <b>None</b> . (void<br>function).                                                 | Reload any<br>software-<br>switched<br>Model-<br>Specific<br>Registers to<br>VM values.                                                                        |

| HVResumeLowLevel                | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.1.1 | None       | <b>None</b> . (Assembly function taking no arguments). Does not return to caller. | Load VM<br>general-<br>purpose<br>register<br>state into<br>CPU,<br>execute VT<br>"vmresume"<br>instruction<br>to actuate<br>switch from<br>VMM to VM          |

VMware, Inc.

| Module Function      | Security<br>Function(s)               | SFR(s)                              | Parameters                                                                                                                | Parameters Return Value                             |                                                                                                                                                                                                                                                   |

|----------------------|---------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HVExitLowLevel       | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.1.1,<br>FPT_VIV_EXT.1.2 | None None. (Assemb<br>function entered<br>directly by<br>hardware). Doe<br>not return to cal<br>as there is no<br>caller. |                                                     | Main exit<br>point from<br>VM back to<br>VMM.<br>Saves VM<br>general-<br>purpose<br>register<br>state from<br>CPU and<br>immediately<br>loads<br>zeroes into<br>most such<br>registers.<br>VMM<br>software is<br>now in<br>control of<br>the CPU. |

| HVVendorSpecificExit | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.1.1,                    | None                                                                                                                      | <b>None</b> . Does not return to caller.            | Saves more<br>VM state,<br>reloads<br>more VMM<br>state.                                                                                                                                                                                          |

| HVMSR_VMExit         | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.1.1                     | None                                                                                                                      | <b>None</b> . (void function).                      | Reloads<br>any<br>software-<br>switched<br>Model-<br>Specific<br>Registers<br>back to<br>VMM<br>values.                                                                                                                                           |

| HVExit               | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.1.1                     | reason - VT<br>exit reason,<br>idtVecInfo -<br>VT-provided<br>IDT<br>vectoring<br>information                             | <b>None</b> (void<br>function), does not<br>return. | Processes<br>exit cause<br>provided by<br>VT, calling<br>various<br>other code<br>to handle<br>each type of<br>exit. (TBD:<br>explain<br>more/better)                                                                                             |

| Module Function | Security<br>Function(s)               | SFR(s)          | Parameters                                                                                                                                                                                                                        | Return Value                                                                                                                                   | Rationale                                                                                                             |

|-----------------|---------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| VVT_VMENTER     | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.1.1 | launch -<br>whether<br>launching<br>(the first<br>entry,<br>before<br>having<br>resumed) or<br>resuming<br>instrLen -<br>the length<br>of the<br>instruction<br>attempting<br>the launch<br>(to advance<br>past, upon<br>success) | An x86fault<br>object pointer,<br>representing<br>either a specific<br>failure, or<br>successful VM<br>entry<br>(X86Fault_None<br>or similar). | Switch to<br>the nested<br>guest<br>VMCS,<br>ready for<br>HV resume<br>into the<br>nested<br>guest, if<br>successful. |

#### 4.1.4.2 Internal Interfaces (Sensitive host fields for context-switch)

| Module Function            | Security<br>Function(s)                | SFR(s)              | VMCS fields<br>protected                                                                                                                                                                                | Parameters | Return<br>Value                            | Rationale                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------|----------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HVVTInitVMCSH<br>ostFields | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_EX<br>T.1.1 | HOST_CS,<br>HOST_ES,<br>HOST_DS,<br>HOST_DS,<br>HOST_TR,<br>HOST_PAT,<br>HOST_CR3,<br>HOST_CR3,<br>HOST_CR3,<br>HOST_GDTRB<br>ASE,<br>HOST_GDTRBA<br>SE,<br>HOST_IDTRBA<br>SE,<br>HOST_RSP,<br>HOST_RIP | None       | None.<br>(void<br>functio<br>n).           | Basic host register<br>state loaded upon HV<br>exit. Static after<br>initialization. Provides<br>program counter<br>(HOST_RIP) to execute<br>HVExitLowLevel, stack<br>pointer (HOST_RSP)<br>and other basic state,<br>automatically switched<br>by VT support in the<br>CPU. Ensures<br>fundamental register<br>state in VMM<br>unaffected by VM<br>values. |

| HV_SetHostCR0              | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_EX<br>T.1.1 | HOST_CR0                                                                                                                                                                                                | None       | hostC<br>R0 -<br>value<br>to set<br>in cr0 | Another fundamental<br>control register loaded<br>upon HV exit.                                                                                                                                                                                                                                                                                             |

| HV_SetHostCR4              | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_EX<br>T.1.1 | HOST_CR4                                                                                                                                                                                                | None       | hostC<br>R4 -<br>value<br>to set<br>in cr4 | Another fundamental<br>control register loaded<br>upon HV exit.                                                                                                                                                                                                                                                                                             |

| Module Function            | Security<br>Function(s)                | SFR(s)              | VMCS fields<br>protected | Parameters                                                  | Return<br>Value                  | Rationale                                                                                                            |

|----------------------------|----------------------------------------|---------------------|--------------------------|-------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|

| HV_SetNestedPa<br>gingRoot | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_EX<br>T.1.1 | EPTP                     | I4MPN -<br>MPN<br>correspondi<br>ng to EPTP<br>to populate. | None.<br>(void<br>functio<br>n). | Sets the VT nested<br>paging root (VMCS<br>field EPTP) to a given<br>value. (See module<br>4.2: VMM guest<br>memory) |

#### 4.1.4.3 Internal Interfaces (Sensitive host field for posted interrupts)

| Module Function          | Security<br>Function(s)               | SFR(s)              | VMCS fields<br>protected   | Parameters | Return<br>Value              | Rationale                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|---------------------------------------|---------------------|----------------------------|------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HVVTInitPostedInterrupts | SF6.Protection<br>of the TSF<br>(FPT) | FPT_VIV_EXT.<br>1.1 | PI_NOTIFY,<br>PI_DESC_ADDR | None       | None.<br>(void<br>function). | Allow VT<br>operation<br>to use<br>posted<br>interrupts<br>without<br>incurring<br>an HV exit<br>when the<br>notification<br>vector is<br>used to<br>raise an<br>inter-<br>processor<br>interrupt<br>from<br>another<br>CPU. If the<br>vector were<br>mis-<br>programme<br>d,<br>interrupts<br>could be<br>dropped,<br>resulting in<br>host<br>stability. |

# 4.1.4.4 Internal Interfaces (Controls determining circumstances causing HV exits)

|                      | -                                      |                     |                                           |            |                                   |                                                                                                                                                                                                                                                                                                                                              |

|----------------------|----------------------------------------|---------------------|-------------------------------------------|------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Module<br>Function   | Security<br>Function(s)                | SFR(s)              | VMCS<br>fields<br>protected               | Parameters | Return Value                      | Rationale                                                                                                                                                                                                                                                                                                                                    |

| HVSetVMCSP<br>inCtl  | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_E<br>XT.1.1 | PIN_VME<br>XEC_CTL                        | None       | <b>None</b> . (void<br>function). | Configures handling (whether<br>to HV exit) of asynchronous<br>events such as interrupts<br>(including host interrupts<br>unrelated to the currently-<br>running VM). Careful<br>programming of these<br>controls guarantees VM<br>interruptibility and allows host<br>software in the TOE (VMM,<br>the vmkernel) to operate<br>effectively. |

| HVSetVMCSC<br>PUCtl  | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_E<br>XT.1.1 | CPU_VME<br>XEC_CTL,<br>2ND_VME<br>XEC_CTL | None       | <b>None</b> . (void<br>function). | Configures handling (whether<br>to HV exit) of synchronous<br>processor events (mostly<br>execution of specific<br>instructions and related<br>circumstances). Used to<br>inhibit direct access to<br>sensitive host resources (e.g.<br>port I/O instructions on the<br>physical CPU) and to<br>otherwise constrain VM<br>execution.         |

| HVSetVMCSE<br>xitCtl | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_E<br>XT.1.1 | VMEXIT_C<br>TL                            | None       | <b>None</b> . (void<br>function). | Configured automatic actions<br>performed by the CPU at VT<br>exit, such as entering long<br>mode (64-bit execution, as<br>requited by the TOE – see<br>VT_REQUIRED_EXIT_CTLS)                                                                                                                                                               |

| HVSetVMCS2<br>ndCtl  | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_E<br>XT.1.1 | 2ND_VME<br>XIT_CTL                        | None       | <b>None</b> . (void function).    | Configured automatic actions<br>performed by the CPU at VT<br>exit (secondary list). For<br>example, whether EPT is<br>enabled (used by module 4.2:<br>VMM HV Memory<br>Management).                                                                                                                                                         |

| HVSetVMCSX<br>CPCtl  | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_E<br>XT.1.1 | XCP_BITM<br>AP                            | None       | <b>None</b> . (void<br>function). | Force #AC exceptions to HV<br>exit. Without this, a CPU can<br>be caught in an infinite #AC<br>loop due to a malicious VM.<br>Force machine checks to exit,<br>to be reported to the host<br>kernel. See also<br>HV_XCP_MASK. Allows<br>other forcing of exceptions to<br>exit, as well.                                                     |

| Module<br>Function       | Security<br>Function(s)                | SFR(s)              | VMCS<br>fields<br>protected  | Parameters                                                                                                                                         | Return Value                      | Rationale                                                                                                                                                                                    |

|--------------------------|----------------------------------------|---------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HVSetMSRBit<br>map       | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_E<br>XT.1.1 | MSRBITM<br>AP                | None                                                                                                                                               | <b>None</b> . (void function).    | Enables bitmap allowing for<br>non-exiting access to specific<br>Model-Specific Registers,<br>which are in turn context-<br>switched in<br>HVExit/HVResume when<br>made accessible this way. |

| HV_SetMSRIn<br>tercept   | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_E<br>XT.1.1 | MSRBITM<br>AP                | bitmap - the<br>bitmap<br>address,<br>msrNum -<br>the MSR to<br>intercept,<br>accessMod<br>e - the<br>read/write<br>access to<br>intercept         | <b>None</b> . (void<br>function). | Denies non-exiting access to<br>a specific Model-Specific<br>Register.                                                                                                                       |

| HV_ClearMSR<br>Intercept | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_E<br>XT.1.1 | MSRBITM<br>AP                | bitmap - the<br>bitmap<br>address,<br>msrNum -<br>the MSR not<br>to intercept,<br>accessMod<br>e - the<br>read/write<br>access not<br>to intercept | <b>None</b> . (void<br>function). | Allows non-exiting access to<br>a specific Model-Specific<br>Register.                                                                                                                       |

| HVSetVMCSE<br>nclsBitmap | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_E<br>XT.1.1 | ENCLS_E<br>XITING_BI<br>TMAP | None                                                                                                                                               | <b>None</b> . (void<br>function). | Enables bitmap allowing for<br>non-exiting execution of<br>ENCLS instruction for some<br>situations. See module 4.8:<br>SGX.                                                                 |

| HVSetVMCSE<br>nclvBitmap | SF6.Protecti<br>on of the<br>TSF (FPT) | FPT_VIV_E<br>XT.1.1 | ENCLV_E<br>XITING_BI<br>TMAP | None                                                                                                                                               | <b>None</b> . (void<br>function). | Enables bitmap allowing for<br>non-exiting execution of<br>ENCLV instruction for some<br>situations. See module 4.8:<br>SGX.                                                                 |

4.1.5 Used interfaces of other modules

| Module Function     | Module                          | Description                                                                                                                                                                                     | Parameters                                                                                                                                                                    | Return<br>Value                                                      | File                                       |

|---------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------|

| HVTryFastExit       | 4.4 Fast<br>Path                | Attempts to<br>handle VT exit<br>information<br>quickly                                                                                                                                         | <b>reason</b> - VT<br>exit reason                                                                                                                                             | None<br>(void<br>function)<br>, does<br>not<br>return if<br>handled. | vmcore/monitor/vmm/hv/vt/hv-<br>common.h   |

| HVTryFastNestedExit | 4.4 Fast<br>Path                | Attempts to<br>handle VT exit<br>information<br>quickly, for<br>inner guest<br>execution                                                                                                        | reason - VT<br>exit reason,<br>idtVecInfo -<br>VT-provided<br>IDT<br>vectoring<br>information                                                                                 | None<br>(void<br>function)<br>, does<br>not<br>return if<br>handled. | vmcore/monitor/vmm/hv/vt/hv-<br>common.h   |

| Interp_Step         | 4.5<br>Instruction<br>Emulation | Emulates one<br>guest<br>instruction,<br>delivering any<br>resulting faults<br>to the guest.<br>Run-time<br>entrypoint to<br>the interpreter.                                                   | None.                                                                                                                                                                         | <b>None</b><br>(void<br>function)                                    | vmcore/monitor/common/cpu/x86/int<br>erp.c |

| MonMSR_SetMSR       | 4.8<br>VMM/VMK<br>interface     | Communicates<br>to switching<br>interface<br>properties of<br>the given MSR<br>(whether it<br>must be<br>reloaded and<br>with what<br>value, when<br>entering/exiting<br>VMM)                   | msr -<br>Model-<br>Specific<br>Register<br>(from short<br>list of<br>allowed<br>values),<br>newVal -<br>new value<br>for MSR,<br>flags -<br>switching<br>reload<br>properties | <b>None</b><br>(void<br>function)                                    | vmcore/public/monMSR.h                     |

| MonMSR_SetMSRUnused | 4.8<br>VMM/VMK<br>interface     | Communicates<br>to the<br>switching<br>interface that<br>the given MSR<br>does not need<br>to be reloaded<br>when entering<br>VMM (VMM<br>can run with<br>any value,<br>without ill<br>effect). | msr -<br>Model-<br>Specific<br>Register<br>(from short<br>list of<br>allowed<br>values)                                                                                       | <b>None</b><br>(void<br>function)                                    | vmcore/public/monMSR.h                     |

# 4.1.6 Mapping to the Source Code

| Function                                               | Description                                                                        | File                                 |

|--------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------|

| HVResume                                               | Entry point for HV resume flow.                                                    | vmcore/monitor/vmm/hv/common/hv.c    |

| HV_StepToSafePointAndResume                            | Corner case for emulation before HV resume.                                        | vmcore/monitor/vmm/hv/common/hv.c    |

| HVVendorSpecificResume                                 | VT-specific HV resume, next step after HVResume                                    | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| HVMSR_VMEnter                                          | Model-Specific Register switch                                                     | vmcore/monitor/vmm/hv/common/hvMSR.c |

| HVResumeLowLevel                                       | Final switch of state and actual transition to VM execution                        | vmcore/monitor/vmm/hv/vt/vtasm.S     |

| HVExitLowLevel                                         | Initial switch from VM execution, save of VM state                                 | vmcore/monitor/vmm/hv/vt/vtasm.S     |

| HVVendorSpecificExit                                   | VT-specific HV exit                                                                | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| HVMSR_VMExit                                           | Model-Specific Register switch                                                     | vmcore/monitor/vmm/hv/common/hvMSR.c |

| HVExit                                                 | General HV exit path, calls out to various handlers for exit reasons               | vmcore/monitor/vmm/hv/common/hv.c    |

| (VMCS field table in VMW notation, no named functions) | Tokens naming VMCS fields<br>used in VMW code and<br>definitions via preprocessing | vmcore/public/x86vt-vmcs-fields.h    |

| HVVTInitVMCSHostFields                                 | Set initial/static VMCS host fields to reload from at HV exit                      | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| HV_SetHostCR0                                          | Set host VMCS %cr0 register field to reload at HV exit                             | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| HV_SetHostCR4                                          | Set host VMCS %cr4 register field to reload at HV exit                             | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| HVVTInitPostedInterrupts                               | Initialize posted interrupt state in VMCS, if enabled.                             | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| HVSetVMCSPinCtl                                        | Set asynchronous event ("PIN") controls.                                           | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| HVSetVMCSCPUCtl                                        | Set synchronous CPU event controls.                                                | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| HVSetVMCS2ndCtl                                        | Set secondary synchronous CPU event controls.                                      | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| HVSetVMCSExitCtl                                       | Set VM exit behaviors.                                                             | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| HVSetVMCSXCPCtl                                        | Set exception exiting controls.                                                    | vmcore/monitor/vmm/hv/vt/hv-vt.c     |

| Function               | Description                                                                                                                                                                                 | File                                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| HVSetMSRBitmap         | Set bitmap of Model-Specific<br>Registers used to determine<br>whether read/write MSR<br>instructions cause VM exits or<br>write to CPU state (requiring<br>context-switching in software). | vmcore/monitor/vmm/hv/vt/hv-vt.c       |

| HV_SetMSRIntercept     | Set access VMM interception<br>(force HV exit) in given MSR<br>bitmap for given MSR and<br>access type.                                                                                     | vmcore/monitor/vmm/public/hvPlatform.h |

| HV_ClearMSRIntercept   | Clear access VMM interception<br>(avoid HV exit) in given MSR<br>bitmap for given MSR and<br>access type.                                                                                   | vmcore/monitor/vmm/public/hvPlatform.h |

| HVSetVMCSEnclsBitmap   | Set bitmap for ENCLS-instruction exiting (see module 4.9: SGX)                                                                                                                              | vmcore/monitor/vmm/hv/vt/hv-vt.c       |

| HVSetVMCSEnclvBitmap   | Set bitmap for ENCLV-instruction exiting (see module 4.9: SGX)                                                                                                                              | vmcore/monitor/vmm/hv/vt/hv-vt.c       |

| HV_SetNestedPagingRoot | Sets the VT nested paging root<br>(VMCS field EPTP) to a given<br>value. (See module 4.2: VMM<br>guest memory)                                                                              | vmcore/monitor/vmm/hv/vt/hv-vt.c       |

| VVT_VMENTER            | Effects a VM entry managed by the current VMCS.                                                                                                                                             | vmcore/monitor/common/hv/vt/vvt.c      |

# 4.1.7 Appendix A: Bibliography for the Intel VT References

| Document                                                                                                           | Author / Company                   | Date       | Notes                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel® 64 and IA-32 Architectures<br>Software Developer's Manual<br>Volume 3C: System Programming<br>Guide, Part 3 | Intel Corporation<br>www.intel.com | 06/30/2022 | Specific citations are in the<br>detail table below. <b>Note:</b><br>Intel renumbers resources<br>over time. These chapters<br>and the SDM volume<br>number are correct as of<br>June 30, 2022. |

| Chapter name                                                                                                       | Content                            |            |                                                                                                                                                                                                 |

| (23) Introduction to Virtual Machine<br>Extensions                                                                 | "VMX" / VT overview                |            |                                                                                                                                                                                                 |

| (24) Virtual Machine Control<br>Structures                                                                         | VMCS definitions                   |            |                                                                                                                                                                                                 |

| (25) VMX Non-Root Operation                                                                                        | Guest operation                    |            |                                                                                                                                                                                                 |

| (26) VM Entries                                                                                                    | Transitions from VMM to VM         |            |                                                                                                                                                                                                 |

| (27) VM Exits                                                                                                      | Transitions from VM to VMM         |            |                                                                                                                                                                                                 |

**vm**ware<sup>®</sup>

#### 4.1.8 Appendix B: Navigating HV module code

The code and header files implementing the HV module are used across multiple products and CPU architectures. Only a subset of the code is of relevance to the TOE. This table endeavors to simplify reading code and header files by explaining what is included and excluded from the TOE. Terminology clarifying the above documentation is also provided.

| Term or token            | Meaning                                                              | Included in TOE? |

|--------------------------|----------------------------------------------------------------------|------------------|

| vmx86_server             | Set to 1 if building ESX                                             | Yes              |

| VMX86_SERVER (CPP token) | #defined if building ESX                                             | Yes              |

| SERVER_ONLY()            | Macro contents defined if building ESX                               | Yes              |

| HOSTED_ONLY()            | Not relevant to ESX, enclosed contents omitted                       | No               |

| vmx86_vmm                | Set to 1 if building VMM                                             | Yes              |

| vmx86_ulm                | Set to 0 if building VMM                                             | No               |

| ULM_ONLY()               | Not relevant to ESX, enclosed contents omitted                       | No               |

| vmx86_release            | Set to 1 if building for releases to customers                       | Yes              |

| vmx86_debug              | Set to 1 if building for debug builds                                | No               |

| vmx86_devel              | Set to 1 if building for internal developers                         | No               |

| vmx86_vt                 | Set to 1 if building for VT support                                  | Yes              |

| vmx86_svm                | Not relevant to VT support (AMD-specific)                            | No               |

| VCPU_InGuestOperation()  | Returns TRUE if the VCPU is running or<br>emulating the nested guest | Yes              |

#### 4.2 VMM HV Memory Management (SFR-ENFORCING)

The VMM HV Memory Management (hereafter "guest memory") module implements management of memory pages accessible to the virtual machine domain (guest OS, hereafter "VM") while it executes in HV (via module 4.1: VMM Hardware Virtualization) or emulation (via module 4.5: VMM Instruction Emulation).

# **vm**ware<sup>®</sup>

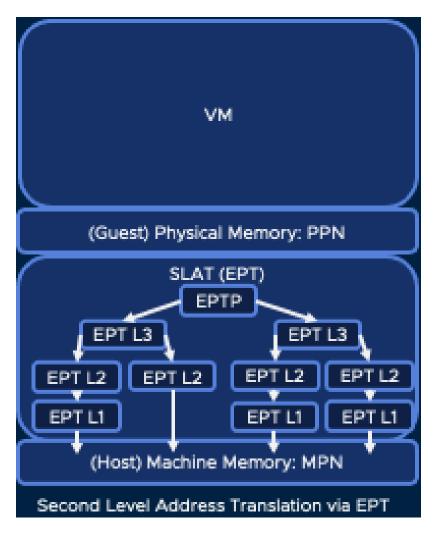

Intel provides a technology for Second Level Address Translation ("SLAT") known as Extended Page Tables (hereafter "EPT"). EPT is a hierarchical system of translation via page tables: 4 kilobyte pages of 512 64-bit Extended Page Table Entries (hereafter "EPTEs") apiece, from a root known as the Extended Page Table Pointer (hereafter "EPTP") on to some terminal EPTE. ETPEs also encode access permissions. Intel describes EPT in the Intel Software Developers Manual, Volume 3C: System Programming Guide, Part 3, Chapter 28 (See 4.2.7 Appendix A below).

The guest memory module manages views of guest physical memory using EPT. When the VM executes via Intel's VT (see 4.1: VMM Hardware Virtualization), the guest memory module provides this view of guest physical memory for a given VCPU via an EPTP. The EPT tree translates between guest Physical Page Numbers (hereafter "PPNs") and host Machine Page Numbers (hereafter "MPNs") or non-present entries. When in VT, a memory access will obey the programmed EPT tree and result in either a successful, fast memory access or an HV exit to VMM.

Because the guest domain can directly access host memory (as provided, constrained and prescribed by the TOE), this module is SFR-enforcing. The module must provide only the correct pages of host memory, and guarantee that access is correctly constrained.

The guest memory module programs the EPT tree with pages of memory and permissions. The guest memory module interfaces with the host memory allocator (see 9.5: "VM Volatile Memory Virtualization") to acquire the correct page and any constraining page permissions.

Version 1.0

The memory allocator module may also request that the guest memory module relinquish access to a page.

The guest memory module, vmKernel memory modules and other virtualization modules use an intermediate representation of memory known as the "memory bus" (or "BusMem") to prioritize what type of resource is visible for a given PPN. It is possible, for example, to layer a virtual device (e.g. SVGA) on top of non-volatile memory, such that an access to a particular PPN should exit to VMM and be handled by SVGA device code. The BusMem system denominates pages in BusMem Page Numbers (hereafter "BPNs"). In the conversion of a PPN to an MPN, the memory bus is traversed.

For efficiency, contiguous, aligned sets of PPNs of size 512 or 512 \* 512 with identical permissions may be promoted to a larger page size. Thus 512 aligned, contiguous 4 kilobyte pages mapped at level 1 of EPT may be replaced with one 2 megabyte page at level 2 of EPT, and 512 aligned, contiguous 2 megabyte pages mapped at level 2 of EPT may be replaced with one 1 gigabyte page at level 3 of EPT. If permissions on a subpage of any larger (2 megabyte, 1 gigabyte) page are then modified, the larger page is invalidated. Such optimizations add complexity to the module, but do not violate its security guarantees, as protections are always enforced conservatively and correctly for every page.

EPT uses Translation Lookaside Buffers (EPT "TLBs" hereafter) in the CPU to ensure high performance. These caches are tagged with Virtual Process Identifiers (hereafter "VPIDs"). As such, the module must follow cache coherency protocols when unmapping or modifying mappings in EPTEs. The guest memory module coordinates with the VMM-VMK Entry module (see 4.8) to ensure proper switching and flushing of EPT TLBs and VPIDs when switching between VMs.

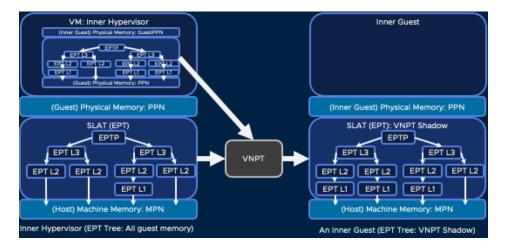

The HV module (see 4.1: VMM Hardware Virtualization) implements virtualization of Hardware Virtualization (VHV) via virtualization of Intel's VT technology (VVT). The guest memory module provides complementary technology to virtualize guest memory via virtualization of Intel's EPT, implemented as Virtualization of Nested Page Tables (hereafter VNPT). When a VM uses VVT, its inner hypervisor describes execution of its inner guests via VT semantics. When a VM uses VVT, its inner hypervisor may use VNPT, describing inner guest memory via EPT semantics. VNPT converts inner hypervisor description of inner guest memory to a host-level EPT tree known as a VNPT shadow, for efficient execution. VNPT shadows are composed of strict subsets of a VM's primary EPT tree, with page protections at least as restrictive. Thus each VCPU can either run with the VM-global EPT tree or one of its subsets, a VNPT shadow.

The guest memory module also maintains parallel x86 page table trees used to enable fast emulation of guest memory accesses. These trees, known as the trace tree and no-trace tree, map views of guest physical memory into VMM. These trees are not SFR-enforcing as they do not directly expose memory to the guest, but they are noteworthy in support of other modules (e.g. 4.5: VMM Instruction Emulation).

#### 4.2.1 Security Functionality (SF)

See the table in Section 4.2.2.

#### 4.2.2 Security Functional Requirement (SFR)

| Security Function (SF)             | Security Function Requirement (SFR) | Rationale                                                                                                                                                                                                                            |

|------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SF6.Protection of the TSF<br>(FPT) | FPT_VIV_EXT.1.1                     | The TSF shall maintain a security domain for<br>the execution of each virtual machine that<br>protects the virtual machine from interference<br>and tampering by untrusted subjects or<br>subjects from outside the scope of the VM. |

#### 4.2.3 Provided TSFI

This module has no TSFI as it is an internal module and has no exposure to outside the TOE.

#### 4.2.4.1 Internal Interfaces of the Module (General execution)